開漏輸出解析

一、開漏與開集輸出

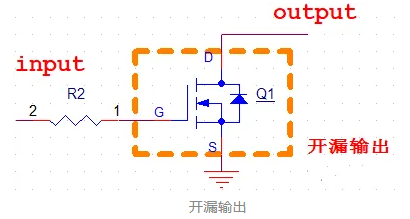

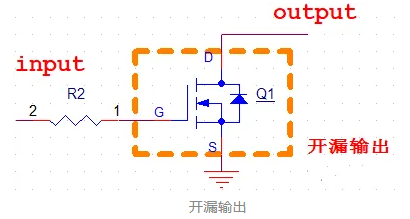

在電子電路設計中,開漏(OD)輸出和開集(OC)輸出是兩種常見的輸出配置。當使用 MOS 管作為輸出器件時,被稱為開漏輸出,其輸出引腳即為 MOS 管的漏極。

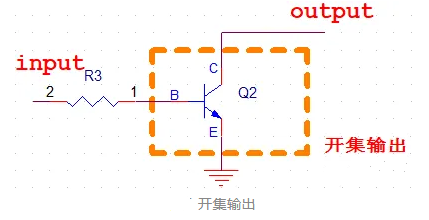

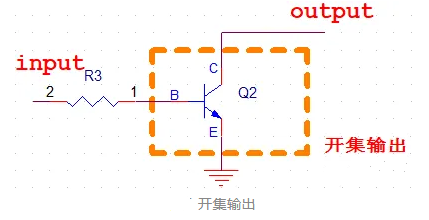

而當以三極管作為輸出器件時,則稱為開集輸出,輸出引腳為三極管的集電極。由于 MOS 管在眾多應用場景中更為普遍,因此通常使用 “開漏輸出” 這一術語來泛指這兩種輸出方式。

而當以三極管作為輸出器件時,則稱為開集輸出,輸出引腳為三極管的集電極。由于 MOS 管在眾多應用場景中更為普遍,因此通常使用 “開漏輸出” 這一術語來泛指這兩種輸出方式。

二、開漏輸出的特性

(一)高電平需外部驅動

開漏輸出最顯著的特性之一是其在輸出高電平時缺乏自身的驅動能力。這意味著僅依靠開漏輸出電路本身,無法直接提供穩定的高電平信號。為解決這一問題,需在漏極或集電極外部接入上拉電阻,連接至相應的電源電平。通過上拉電阻,當輸出器件截止時,外部電源可通過上拉電阻為輸出端提供高電平,從而使開漏輸出具備完整的高低電平輸出功能。

(二)電平調節的靈活性

開漏輸出的另一大優勢在于其輸出電平的靈活性。輸出電平的高低完全由上拉電阻所連接的電源電壓決定。這一特性使得開漏輸出在不同電平系統之間進行接口連接時極為便利,尤其是在需要進行電平轉換的場合。例如,在將低電壓的微控制器與高電壓的外圍設備進行連接時,只需調整上拉電阻的電源電壓,即可實現電平的匹配,而無需復雜的電平轉換電路。

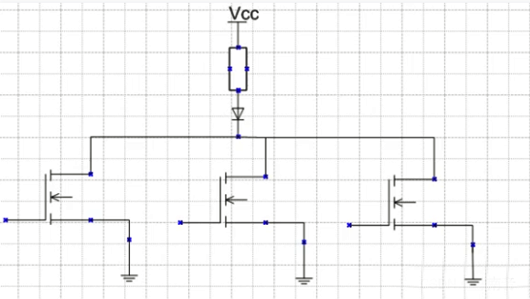

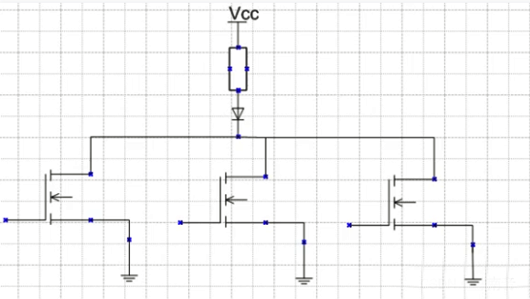

(三)便于實現 “線與” 邏輯

開漏輸出在數字邏輯電路中,為實現 “線與” 邏輯功能提供了極大的便利。所謂 “線與”,是指將多個信號線直接連接在一起,形成一條總線。在這種連接方式下,只有當所有連接的信號線輸出均為低電平時,總線呈現高電平;只要有一個或多個信號線輸出為高電平,總線則呈現低電平。多個開漏輸出信號連接到同一條總線上時,可通過各自的輸出狀態共同決定總線的電平狀態,從而實現 “線與” 邏輯功能,這在如 I2C 總線等多主多從通信協議中得到了廣泛應用。

三、開漏輸出電路原理與應用

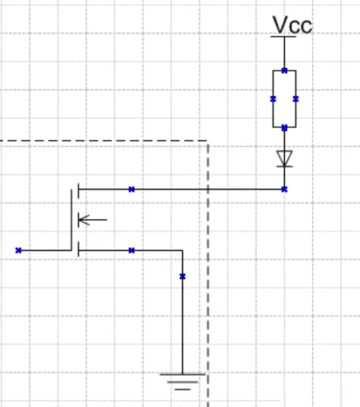

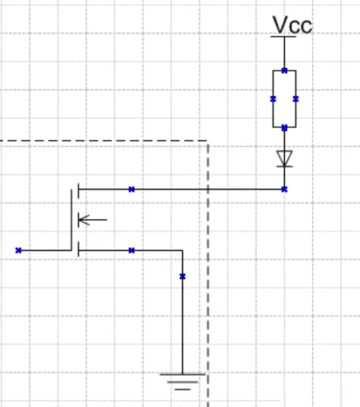

(一)電路結構

開漏輸出電路的核心是將場效應管的漏極直接引出作為輸出引腳。場效應管在電路中通常工作在飽和區或截止區。當需要輸出低電平時,場效應管導通,將輸出引腳拉低至接近地電位;當需要輸出高電平時,場效應管截止,此時輸出引腳處于高阻態,由外部上拉電阻和電源共同作用提供高電平。

(二)電平匹配功能

在實際電路設計中,不同芯片或設備的邏輯電平往往存在差異。例如,某些微控制器的工作電壓可能為 3.3V,而與其連接的外圍設備可能需要 5V 的邏輯電平。在這種情況下,開漏輸出模式能夠發揮其電平匹配的優勢。通過選擇適當的外部上拉電源電壓,可以將開漏輸出的高電平轉換為目標電平,從而實現不同電平系統之間的無縫連接。

(三)減輕 MCU 負擔

從微控制器單元(MCU)的角度來看,使用開漏輸出模式能夠有效減輕其負擔。由于開漏輸出的高電平由外部電源提供,MCU 無需直接驅動輸出引腳至高電平,從而降低了 MCU 的驅動電流需求,有助于提高整個系統的穩定性和可靠性。

(四)“線與” 邏輯的應用實例

在 I2C 總線通信中,多個設備共享同一條數據總線。每個設備的開漏輸出引腳連接到該總線上。當某個設備需要發送低電平時,其開漏輸出的場效應管導通,將總線拉低;而當所有設備均不發送低電平(即場效應管均截止)時,總線通過上拉電阻連接到電源,呈現高電平。通過這種方式,多個設備可以在總線上進行協同通信,實現數據的傳輸與共享。這種 “線與” 邏輯的實現方式,使得 I2C 總線能夠在簡單的硬件基礎上,支持多設備通信,降低了硬件成本和復雜度。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280