mos管上拉電阻與下拉電阻區別詳解

在電子電路設計領域,上拉電阻與下拉電阻是兩種基礎卻極為關鍵的元件,它們在電路中扮演著至關重要的角色,主要作用是將不確定的電平信號固定為穩定的高電平或低電平,確保電路的穩定運行。

在電子電路設計領域,上拉電阻與下拉電阻是兩種基礎卻極為關鍵的元件,它們在電路中扮演著至關重要的角色,主要作用是將不確定的電平信號固定為穩定的高電平或低電平,確保電路的穩定運行。

一、基礎概念

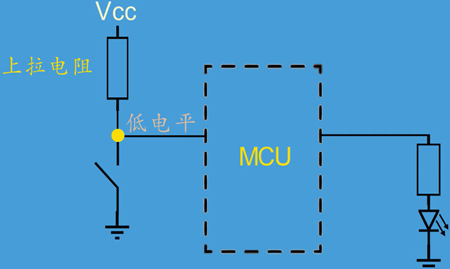

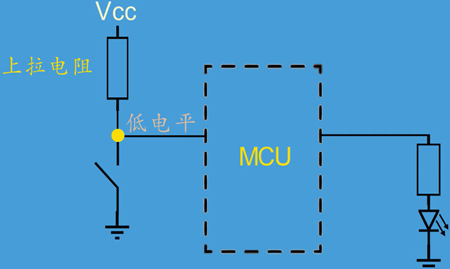

(一)上拉電阻

上拉電阻通過將一個不確定信號與電源 VCCQ 相連,利用電阻將電平穩定在高電平狀態。其原理是當電路中存在不確定信號時,電流通過電阻從電源流向信號端,從而使信號端的電平被 “拉高” 至接近電源電壓的高電平。這種上拉操作實際上是向器件注入電流,為電路提供穩定的高電平信號。當一個帶有上拉電阻的 IO 端口設置為輸入狀態時,其常態表現為高電平,這是因為上拉電阻持續將信號端維持在高電平狀態,除非有其他外部因素(如下拉電路或低電平信號源)將其電平拉低。

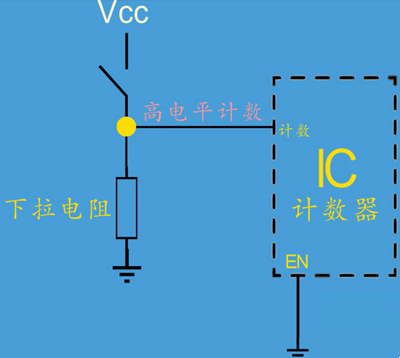

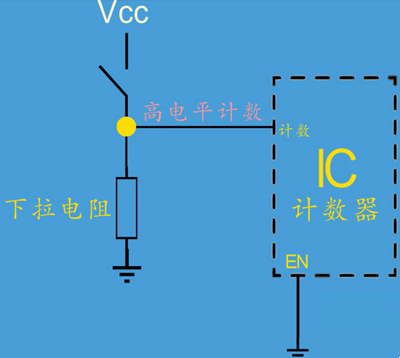

(二)下拉電阻

下拉電阻則是將不確定信號與地 GND 相連,通過電阻將電平固定在低電平。當信號端存在不確定信號時,電流從信號端流向地,從而使信號端的電平被 “拉低” 至接近地電平的低電平狀態。下拉電阻的作用是從器件輸出電流,確保信號端在無其他驅動因素時保持低電平。帶有下拉電阻的 IO 端口在設置為輸入狀態時,常態呈現低電平,因為下拉電阻持續將信號端電平拉低,除非有外部因素(如上拉電路或高電平信號源)將其電平拉高。

二、MOS 管開關電路中的應用

在 MOS 管開關電源電路中,上拉電阻和下拉電阻有著特定的使用場景和重要作用。

(一)應用場景

當遇到前級電路輸出電壓幅度不足的情況時,上拉電阻和下拉電阻可以有效地對電平進行調整。例如,若前級電路只能輸出 0V-3V 的電平,而后級系統需要 0V-5V 的高電平或低電平,上拉電阻可以強制拉高前級的輸出電壓,使其達到 3V-5V 之間的電平,從而滿足后級系統對高電平的要求。同樣地,當下級電路對低電平的要求更為嚴格時,下拉電阻能夠將低電平進一步拉低,具體的拉低幅度取決于所選用的電阻阻值。

(二)具體作用

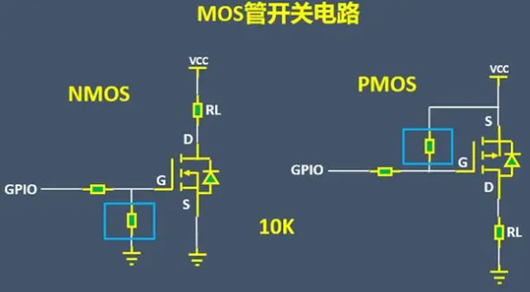

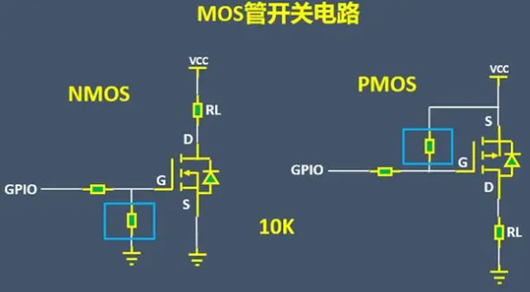

在 MOS 管開關電路中,通常會在 NMOS 管上加一個下拉電阻,而在 PMOS 管柵上加一個上拉電阻,阻值一般在 10KΩ 左右。

這些電阻在電路中主要起到以下三個關鍵作用:

這些電阻在電路中主要起到以下三個關鍵作用:

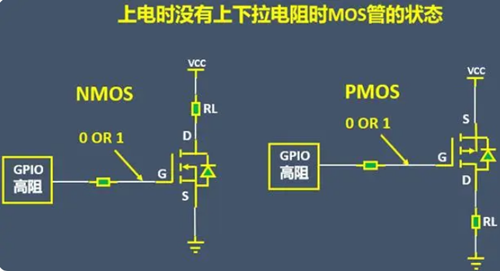

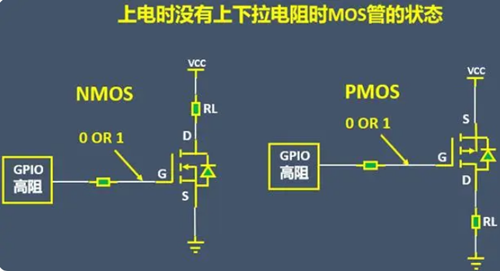

確定 MOS 管柵極電平 :MOS 管在上電瞬間會呈現高阻態,這種狀態下柵極電平不確定,容易受到外界干擾。上拉電阻和下拉電阻可以確保 MOS 管柵極處于一個確定的電平狀態,避免其因高阻態而受到干擾。對于 NMOS 管,下拉電阻使其柵極在無驅動信號時保持低電平,確保管子處于關閉狀態;對于 PMOS 管,上拉電阻則使其柵極在無驅動信號時保持高電平,同樣確保管子關閉。這樣,MOS 管在上電時會一直保持關閉狀態,直到單片機或其他控制單元發出控制信號來改變其狀態。

防止靜電擊穿 :在 MOS 管柵極與源極之間存在寄生電容,當 MOS 管處于高阻態時,容易積累靜電電荷。一旦靜電電壓超過 MOS 管的耐壓值,就可能導致柵極擊穿,損壞器件。上拉電阻和下拉電阻可以為這些積累的靜電電荷提供一個泄放路徑,使柵極電平保持穩定,防止靜電擊穿的發生。

提供放電路徑 :MOS 管的柵極與源極之間的寄生電容在斷電時需要進行放電。上拉電阻和下拉電阻能夠為這些寄生電容提供放電路徑,確保電路斷電后 MOS 管能夠快速、安全地釋放儲存的電荷,避免因電荷殘留導致的電路異常或器件損壞。

三、總結

上拉電阻和下拉電阻在電路設計中起著至關重要的作用。上拉電阻的主要目的是確保 GPIO(低電平有效)在無信號輸入時輸入端的電平為高電平,防止因信號不確定而導致的電路誤動作。相反地,下拉電阻則是為了保證 GPIO(高電平有效)在無信號輸入時輸入端的電平為低電平,同樣是為了避免電路誤動作,確保電路的穩定運行。

通過合理地使用上拉電阻和下拉電阻,可以有效地解決電路中因不確定電平信號引發的問題,提升電路的可靠性和穩定性,確保電子設備在各種工況下的正常運行。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280